FPGA y validación: cuando diseñar para demostrar deja de ser opcional

En muchos artículos anteriores de este blog he insistido en una idea que suele generar cierta incomodidad en proyectos industriales complejos:

la validación no es una fase final, sino una decisión de diseño que condiciona la arquitectura desde el inicio.

Este principio es transversal a la ingeniería de sistemas y aplica tanto a software como a hardware, automatización, simulación o integración de sistemas safety-critical. Sin embargo, hay entornos tecnológicos donde esta afirmación deja de ser una recomendación metodológica para convertirse en una condición de viabilidad técnica.

El desarrollo de sistemas basados en FPGA es uno de esos entornos.

No porque la FPGA sea “más avanzada” o “más difícil” que otras tecnologías, sino porque hace explícitas —y penaliza con rapidez— decisiones arquitectónicas que en otros dominios pueden permanecer ocultas durante demasiado tiempo.

En lógica programable, diseñar para validar no es opcional. Y validar tarde no es solo caro: en muchos casos es arquitectónicamente inviable.

Validación como criterio estructural en sistemas FPGA

Una FPGA no ejecuta instrucciones de forma secuencial.

Implementa comportamiento concurrente, cableado lógicamente, condicionado por dominios de reloj, restricciones temporales y recursos físicos finitos.

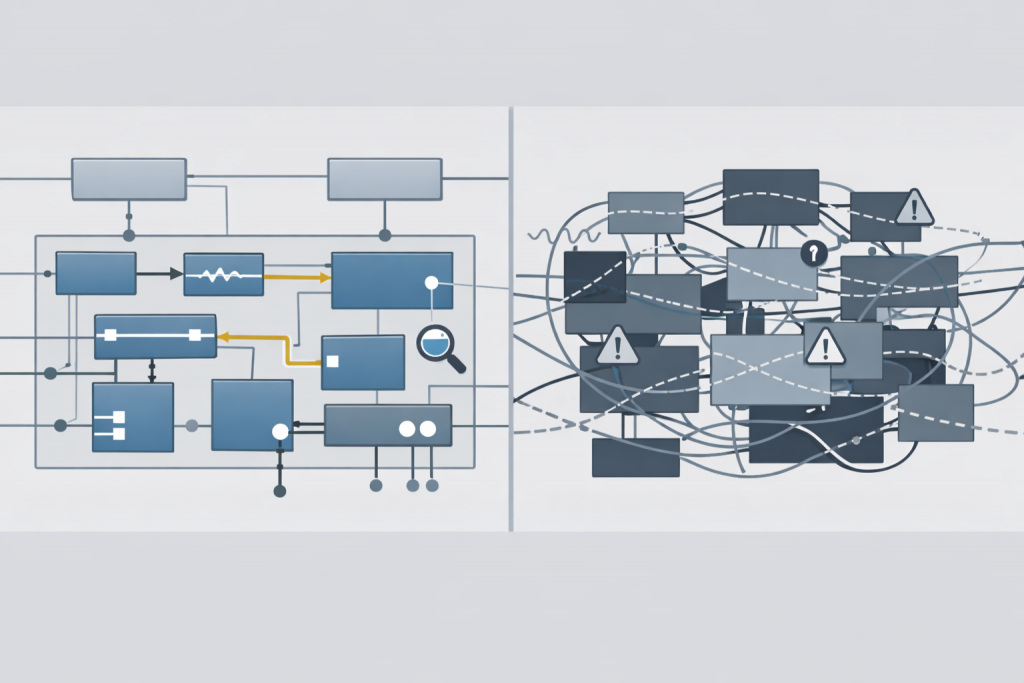

Esto tiene una consecuencia directa:

el sistema no “se deja observar” de forma natural si no ha sido concebido para ello.

En software, todavía es posible añadir trazas, logs o instrumentación avanzada cuando aparecen problemas. En FPGA, cada señal adicional consume recursos, ancho de banda de depuración o pines físicos. La observabilidad no es infinita ni gratuita.

Por eso, en lógica programable, el principio de validación como criterio estructural deja de ser una buena práctica para convertirse en una condición de diseño:

- o el sistema se concibe desde el inicio para ser demostrable,

- o parte de su comportamiento quedará opaco cuando más falta haga entenderlo.

Concurrencia y validación incremental: del principio al HDL

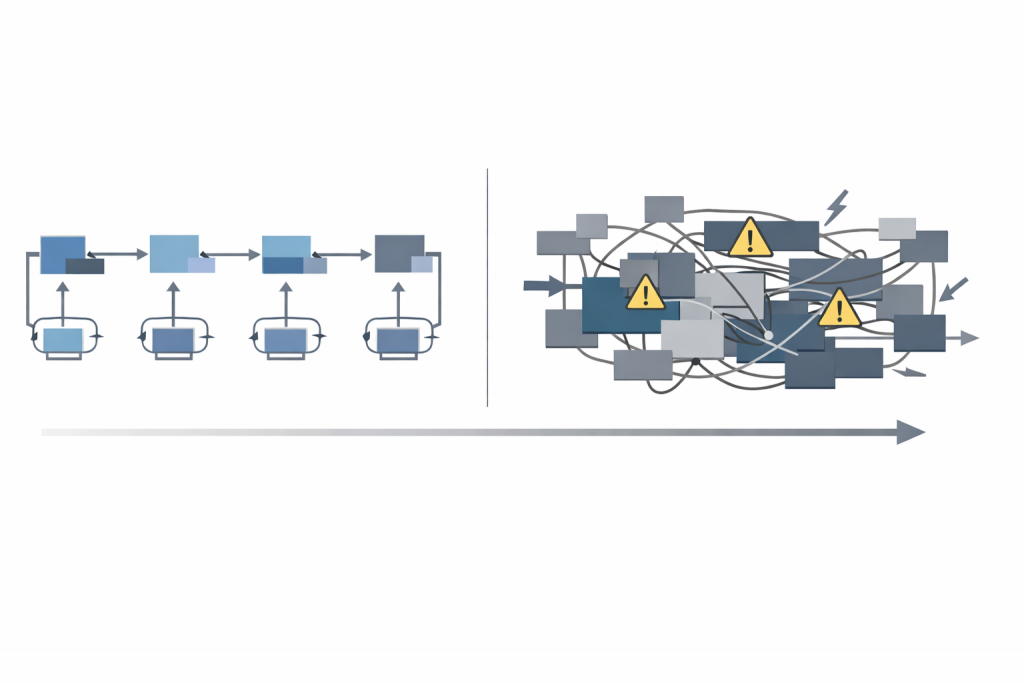

En proyectos complejos suele afirmarse que la validación debe ser incremental.

En FPGA, esta afirmación no es discutible: es la única forma realista de reducir el espacio de estados del sistema.

Un diseño HDL típico está formado por:

- bloques concurrentes,

- máquinas de estados,

- pipelines,

- interfaces que interactúan en paralelo.

Integrar todo sin haber validado previamente los bloques aislados no acelera el proyecto. Amplifica la incertidumbre y desplaza el riesgo hacia fases donde el diagnóstico es más costoso y menos preciso.

La validación incremental en FPGA se traduce de forma muy concreta en:

- testbenches específicos por módulo,

- validación de bloques concurrentes en aislamiento,

- integración progresiva bajo un mismo dominio de reloj,

- análisis explícito de interacciones entre dominios (CDC).

Aquí, la ingeniería de sistemas deja de ser un concepto abstracto y se materializa directamente en el flujo de diseño HDL.

Temporalidad: cuando el tiempo también es arquitectura

En sistemas basados en FPGA, el tiempo no es un efecto colateral del diseño: es parte de la arquitectura.

Latencias, secuencias, sincronizaciones, jitter y márgenes temporales condicionan el comportamiento tanto como la lógica funcional. Validar que “funciona” sin validar cuándo, con qué márgenes y en qué condiciones es una forma incompleta —y peligrosa— de validación.

Por eso, en FPGA, la validación debe integrar desde el inicio:

- simulación funcional,

- simulación temporizada,

- análisis de timing estático,

- restricciones de temporización como artefactos de validación implícita.

Cuando estos elementos se tratan como pasos finales, los problemas no desaparecen: simplemente se manifiestan cuando ya no es posible corregirlos sin reabrir la arquitectura.

En este contexto, una afirmación se vuelve especialmente clara:

en FPGA, no validar el timing desde el inicio no retrasa la validación; la invalida.

Observabilidad: si no se puede ver, no se puede demostrar

Uno de los principios recurrentes en la validación de sistemas complejos es la demostrabilidad: la capacidad de explicar y evidenciar por qué el sistema se comporta como lo hace.

En FPGA, esta capacidad no se improvisa.

No existe un “printf” trivial. Cada punto de observación debe diseñarse, justificarse y mantenerse a lo largo del ciclo de vida del sistema. La depuración en hardware real es intrínsecamente limitada si no se han previsto:

- registros de estado,

- contadores de eventos,

- flags de error,

- señales de salud internas,

- integración planificada con analizadores lógicos internos.

Esto refuerza un principio que en otros dominios puede parecer obvio, pero que en FPGA se vuelve estructural:

si no se puede observar, no se puede validar; y si no se diseña para observar, no se podrá demostrar.

Aislamiento y arquitectura orientada a validación

La validación incremental solo es viable si la arquitectura permite aislar subsistemas de forma controlada.

En FPGA, esto se traduce en decisiones arquitectónicas muy concretas:

- interfaces bien definidas,

- particiones claras del diseño,

- posibilidad de sustituir el entorno real por modelos de simulación,

- separación entre lógica específica y lógica de infraestructura.

Sin este aislamiento, cada fallo se propaga a múltiples bloques y se vuelve difícil de atribuir. El resultado es conocido en proyectos industriales: problemas que aparecen “tarde”, durante integración avanzada o incluso en campo, y que en realidad estaban latentes desde el diseño inicial.

La arquitectura orientada a validación no elimina la complejidad, pero la estructura.

El coste real de validar tarde en FPGA

En sistemas safety-critical y de larga vida, el coste de corregir defectos tardíos no es solo económico. Es estructural.

En FPGA, validar tarde implica:

- re-síntesis y nuevo cierre de timing,

- repetición de campañas de ensayo,

- impacto en certificación y recualificación,

- riesgos de obsolescencia de herramientas, placas o IPs.

Pero el problema más serio no es el coste directo, sino que no todos los cambios son compatibles con la arquitectura ya cerrada. Hay decisiones que, una vez tomadas, no admiten corrección local sin afectar a todo el sistema.

Aquí se refuerza la tesis central de este blog:

cuando los fallos aparecen solo al final, el problema no es de test; es de arquitectura y estrategia de validación.

Tensiones y límites del encuadre FPGA

Conviene explicitar también los límites de este razonamiento.

No todos los sistemas FPGA son safety-critical ni de larga vida. En prototipos o productos de consumo, el coste de retrabajo puede ser asumible. Además, las FPGAs modernas ofrecen herramientas de depuración avanzadas que mitigan parcialmente las dificultades de validación tardía.

Del mismo modo, existen dominios de software embebido donde las restricciones de certificación y arquitectura son igualmente severas.

Sin embargo, incluso con estas matizaciones, la lógica programable sigue siendo uno de los entornos donde más claramente se observa una realidad incómoda para muchos proyectos:

la validación tardía no falla por falta de esfuerzo, sino porque el sistema no fue diseñado para ser validado.

FPGA como laboratorio conceptual de ingeniería de sistemas

La FPGA no es especial por ser más compleja, sino porque hace visibles las consecuencias de las decisiones tempranas.

Por eso, más allá de su uso tecnológico concreto, es un excelente laboratorio conceptual para una idea central de la ingeniería de sistemas:

solo aquello que se diseña para ser validado puede sostenerse, demostrarse y mantenerse a lo largo del tiempo.

En FPGA, esta idea no es una opinión.

Es una condición de posibilidad.